### TD1457C

### **General Description**

The TD1457C is a high frequency step-down switching regulator with integrated internal highside high voltage power MOSFET. It provides 2A output with current mode control for fast loop response and easy compensation.

The wide 9V to 40V input range accommodates a variety of step-down applications, including those in automotive input environment. A  $1\mu A$  shutdown mode supply current allows use in battery-powered applications.

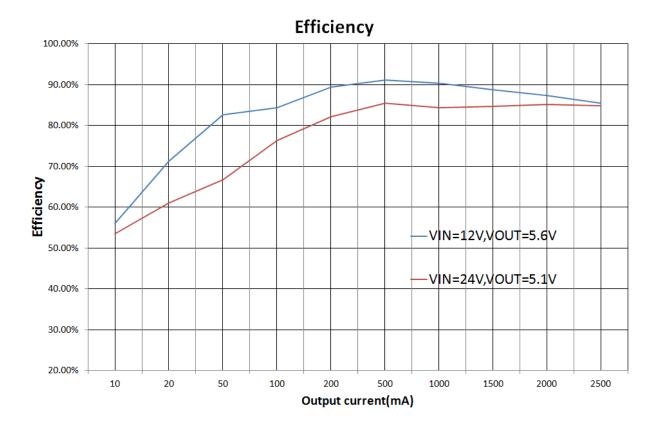

High power conversion efficiency over a wide load range is achieved by scaling down the switching frequency at light load condition to reduce the switching and gate driving losses.

The frequency foldback helps prevent inductor current runaway during startup and thermal shutdown provides reliable, fault tolerant operation.

The TD1457C is available in ESOP8 package.

### **Features**

- Wide 9V to 40V Operating Input Range

- 250mΩ Internal Power MOSFET

- Up to 1MHz Programmable Switching Frequency

- 180µA Quiescent Current

- Ceramic Capacitor Stable

- Internal Soft-Start

- Up to 95% Efficiency

- Output Adjustable from 0.8V to 34V

- Available in ESOP8 PbFree Package

### **Application**

- High Voltage Power Conversion

- Automotive Systems

- Industrial Power Systems

- Distributed Power Systems

- Battery Powered Systems

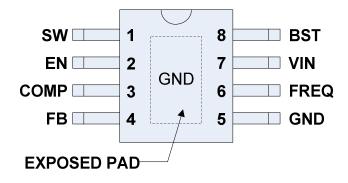

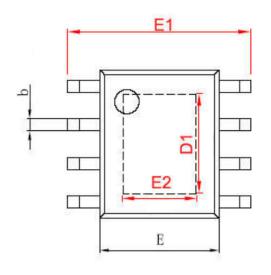

### **Pin Configurations**

(Top view)

TD1457C

### **Pin Description**

| Pin Number | Pin Name | Description                                                                                         |

|------------|----------|-----------------------------------------------------------------------------------------------------|

| 1          | CVA      | Switch Node. This is the output from the high-side switch. A low VF Schottky rectifier to ground    |

| 1          | SW       | is required. The rectifier must be close to the SW pins to reduce switching spikes.                 |

| 2          | EN       | Enable Input. Pulling this pin below the specified threshold shuts the chip down. Pulling it up     |

| 2          | EN       | above the specified threshold or leaving it floating enables the chip.                              |

| 3          | COMP     | Compensation. This node is the output of the GM error amplifier. Control loop frequency             |

| 3          | COMP     | compensation is applied to this pin.                                                                |

|            |          | Feedback. This is the input to the error amplifier. An external resistive divider connected         |

| 4          | FB       | between the output and GND is compared to the internal +0.8V reference to set the regulation        |

|            |          | voltage.                                                                                            |

|            | GND,     | Cround It should be connected as close as possible to the output conscitor avoiding the high        |

| 5          | Exposed  | Ground. It should be connected as close as possible to the output capacitor avoiding the high       |

|            | pad      | current switch paths. Connect exposed pad to GND plane for optimal thermal performance.             |

| 6          | FREQ     | Switching Frequency Program Input. Connect a resistor from this pin to ground to set the            |

| 6          | FREQ     | switching frequency.                                                                                |

|            |          | Input Supply. This supplies power to all the internal control circuitry, both BS regulators and the |

| 7          | VIN      | high-side switch. A decoupling capacitor to ground must be placed close to this pin to minimize     |

|            |          | switching spikes.                                                                                   |

| 0          | DCT      | Bootstrap. This is the positive power supply for the internal floating high-side MOSFET driver.     |

| 8          | BST      | Connect a bypass capacitor between this pin and SW pin.                                             |

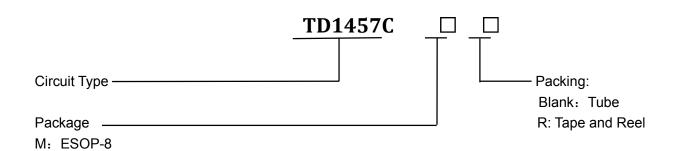

## **Ordering Information**

### TD1457C

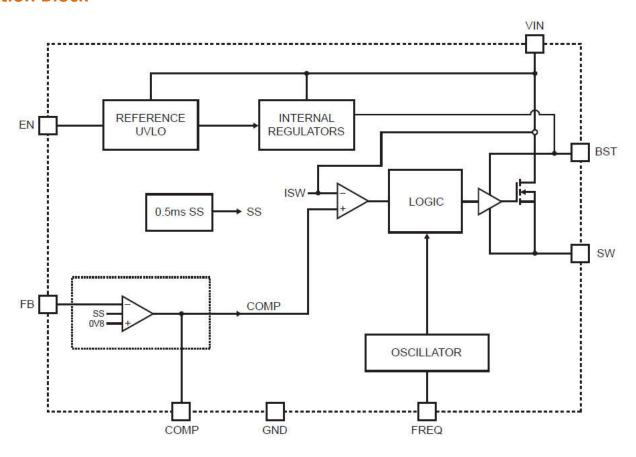

### **Function Block**

Figure 1 Function Block Diagram of TD1457C

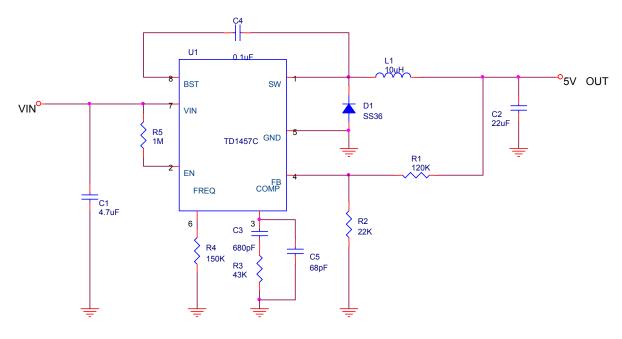

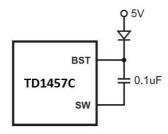

## **Typical Application Circuit**

Figure 2 5V Output Typical Application Schematic

TD1457C

### **Absolute Maximum Ratings** (at T<sub>A</sub>=25°C)

| Symbol           | Parameter                                       | Rating                        | Unit |

|------------------|-------------------------------------------------|-------------------------------|------|

| V <sub>IN</sub>  | Supply Voltage                                  | -0.3 to 40                    | V    |

| $V_{SW}$         | Switch Voltage                                  | -0.5V to V <sub>IN</sub> +0.5 | V    |

|                  | BST to SW                                       | -0.3 to +5                    | V    |

|                  | All other Pins                                  | -0.3 to +5                    | V    |

| ESD              | ESD Susceptibility (Human Body Model)           | 2K                            | V    |

| TJ               | Junction Temperature                            | 150                           | °C   |

| T <sub>SDR</sub> | Maximum Lead Soldering Temperature (10 Seconds) | 260                           | ° C  |

### **Electrical Characteristics**

Unless otherwise specified, these specifications apply over  $V_{IN}$ =12V, $V_{EN}$ =2.5V, $V_{COMP}$ =1.4V,  $T_A$ =25°C Specifications over temperature are guaranteed by design and characterization.

| Characteristics                       | Symbol                | Conditions                      | Min   | Тур   | Max   | Units |

|---------------------------------------|-----------------------|---------------------------------|-------|-------|-------|-------|

| Feedback Voltage                      | $V_{FB}$              | 9V < V <sub>IN</sub> < 40V      | 0.780 | 0.800 | 0.820 | V     |

| Top Switch RDS <sub>(ON) (Note)</sub> | RDS <sub>(ON)-T</sub> | $V_{BST} - V_{SW} = 5V$         | 175   | 250   | 330   | mΩ    |

| Top Switch Leakage                    |                       | $V_{EN} = 0V, V_{SW} = 0V$      | -     | 1     | -     | μΑ    |

| Current Limit                         |                       |                                 | 2.2   | -     | 4.7   | Α     |

| COMP to Current Sense                 | G <sub>CS</sub>       |                                 | -     | 5.7   | -     | A/V   |

| Transconductance                      | U <sub>CS</sub>       |                                 |       |       |       |       |

| Error Amp Voltage Gain                |                       |                                 | -     | 400   | -     | V/V   |

| Error Amp Transconductance            |                       | $I_{COMP} = \pm 3\mu A$         | -     | 120   | -     | μΑ/Α  |

| Error Amp Min Source current          |                       | V <sub>FB</sub> = 0.7V          | -     | 10    | -     | μΑ    |

| Error Amp Min Sink current            |                       | V <sub>FB</sub> = 0.9V          | -     | -10   | -     | μΑ    |

| VIN UVLO Threshold                    |                       |                                 | -     | 7.2   | -     | V     |

| VIN UVLO Hysteresis                   |                       |                                 | -     | 0.5   | -     | V     |

| Soft-Start Time                       |                       | $0V < V_{FB} < 0.8V$            | -     | 0.5   | -     | ms    |

| Oscillator Frequency                  |                       | $R_{FREQ} = 150k\Omega$         | 0.6   | -     | 0.8   | MHz   |

| Minimum Switch On Time                |                       |                                 | -     | 100   | -     | ns    |

| Shutdown Supply Current               |                       | V <sub>EN</sub> < 0.3V          | -     | 1     | 3     | μΑ    |

| Quiescent Supply Current              |                       | No load, V <sub>FB</sub> = 0.9V | -     | 180   | -     | μΑ    |

| Thermal Shutdown                      |                       | Hysteresis = 20°C               | -     | 150   | -     | °C    |

| Minimum Off Time                      |                       |                                 | -     | 100   | -     | ns    |

| Minimum On Time                       |                       |                                 | -     | 100   | =     | ns    |

| EN Up Threshold                       |                       |                                 | 1.3   | -     | 2.2   | V     |

| EN Threshold Hysteresis               |                       |                                 | -     | 200   | -     | mV    |

TD1457C

## **Typical Efficiency**

TD1457C

### **Operation**

The TD1457C is a programmable frequency, non-synchronous, step-down switching regulator with an integrated high-side high voltage power MOSFET. It provides a single highly efficient solution with current mode control for fast loop response and easy compensation. It features a wide input voltage range, internal soft-start control and precision current limiting. Its very low operational quiescent current makes it suitable for battery powered applications.

#### **PWM Control Mode**

At moderate to high output current, the TD1457C operates in a fixed frequency, peak current control mode to regulate the output voltage. A PWM cycle is initiated by the internal clock. The power MOSFET is turned on and remains on until its current reaches the value set by the COMP voltage. When the power switch is off, it remains off for at least 100ns before the next cycle starts. If, in one PWM period, the current in the power MOSFET does not reach the COMP set current value, the power MOSFET remains on, saving a turn-off operation.

#### **Pulse Skipping Mode**

Under light load condition the switching frequency stretches down zero to reduce the switching loss and driving loss.

#### **Error Amplifier**

The error amplifier compares the FB pin voltage with the internal reference (REF) and outputs a current proportional to the difference between the two. This output current is then used to charge the external compensation network to form the COMP voltage, which is used to control the power MOSFET current.

During operation, the minimum COMP voltage is clamped to 0.9V and its maximum is clamped to 2.0V. COMP is internally pulled down to GND in shutdown mode. COMP should not be pulled up beyond 2.6V.

#### **Internal Regulator**

Most of the internal circuitries are powered from the 2.6V internal regulator. This regulator takes the VIN input and operates in the full VIN range. When VIN is greater than

3.0V, the output of the regulator is in full regulation. When  $V_{\text{IN}}$  is lower than 3.0V, the output decreases.

#### **Enable Control**

The TD1457C has a dedicated enable control pin(EN). With high enough input voltage, the chip can be enabled and disabled by EN which has positive logic. Its falling threshold is a precision 1.2V, and its rising threshold is 1.5V (300mV higher).

When EN is pulled down below 1.2V, the chip is put into the lowest shutdown current mode. When EN is higher than zero but lower than its rising threshold, the chip is still in shutdown mode but the shutdown current increases slightly.

#### **Under-Voltage Lockout (UVLO)**

Under-voltage lockout (UVLO) is implemented to protect the chip from operating at insufficient supply voltage. The UVLO rising threshold is about 7.2V while its falling threshold is a consistent 6.5V.

#### **Internal Soft-Start**

The soft-start is implemented to prevent the converter output voltage from overshooting during startup and short circuit recovery. When the chip starts, the internal circuitry generates a soft-start voltage (SS) ramping up from 0V to 2.6V. When it is lower than the internal reference(REF), SS overrides REF so the error amplifier uses SS as the reference. When SS is higher than REF, REF regains control.

#### **Thermal Shutdown**

Thermal shutdown is implemented to prevent the chip from operating at exceedingly high temperatures. When the silicon die temperature is higher than its upper threshold, it shuts down the whole chip. When the temperature is lower than its lower threshold, the chip is enabled again.

#### **Floating Driver and Bootstrap Charging**

The floating power MOSFET driver is powered by an external bootstrap capacitor. This floating driver has its own UVLO protection. This UVLO's rising threshold is 7.2V with a

TD1457C

hysteresis of 150mV. The driver's UVLO is soft-start related. In case the bootstrap voltage hits its UVLO, the soft-start circuit is reset. To prevent noise, there is 20µs delay before the reset action. When bootstrap UVLO is gone, the reset is off and then soft-start process resumes.

The bootstrap capacitor is charged and regulated to about 5V by the dedicated internal bootstrap regulator. When the voltage between the BST and SW nodes is lower than its regulation, a PMOS pass transistor connected from VIN to BST is turned on. The charging current path is from VIN, BST and then to SW. External circuit should provide enough voltage headroom to facilitate the charging.

As long as VIN is sufficiently higher than SW, the bootstrap capacitor can be charged. When the power MOSFET is ON, VIN is about equal to SW so the bootstrap capacitor cannot be charged. When the external diode is on, the difference between VIN and SW is largest, thus making it the best period to charge. When there is no current in the inductor, SW equals the output voltage VOUT so the difference between VIN and  $V_{\text{OUT}}$  can be used to charge the bootstrap capacitor.

At higher duty cycle operation condition, the time period available to the bootstrap charging is less so the bootstrap capacitor may not be sufficiently charged.

In case the internal circuit does not have sufficient voltage and the bootstrap capacitor is not charged, extra external circuitry can be used to ensure the bootstrap voltage is in the normal operational region. Refer to External Bootstrap Diode in Application section.

The DC quiescent current of the floating driver is about  $20\mu A$ . Make sure the bleeding current at the SW node is higher than this value, such that:

$$I_0 + \frac{V_0}{(R1 + R2)} > 20\mu A$$

#### **Current Comparator and Current Limit**

The power MOSFET current is accurately sensed via a current sense MOSFET. It is then fed to the high speed current comparator for the current mode control purpose. The current comparator takes this sensed current as one of its inputs. When the power MOSFET is turned on, the comparator is first blanked till the end of the turn on transition to avoid noise issues. The comparator then

compares the power switch current with the COMP voltage. When the sensed current is higher than the COMP voltage, the comparator output is low, turning off the power MOSFET. The cycle-by-cycle maximum current of the internal power MOSFET is internally limited.

#### **Short Circuit Protection**

When the output is shorted to the ground, the switching frequency is folded back and the current limit is reduced to lower the short circuit current. When the voltage of FB is at zero, the current limit is reduced to about 50% of its full current limit. When FB voltage is higher than 0.4V, current limit reaches 100%.

In short circuit FB voltage is low, the SS is pulled down by FB and SS is about 100mV above FB. In case the short circuit is removed, the output voltage will recover at the SS pace. When FB is high enough, the frequency and current limit return to normal values.

#### Startup and Shutdown

If both VIN and EN are higher than their appropriate thresholds, the chip starts. The reference block starts first, generating stable reference voltage and currents, and then the internal regulator is enabled. The regulator provides stable supply for the remaining circuitries.

While the internal supply rail is up, an internal timer holds the power MOSFET OFF for about  $50\mu s$  to blank the startup glitches. When the internal soft-start block is enabled, it first holds its SS output low to ensure the remaining circuitries are ready and then slowly ramps up.

Three events can shut down the chip: EN low, VIN low and thermal shutdown. In the shutdown procedure, power MOSFET is turned off first to avoid any fault triggering. The COMP voltage and the internal supply rail are then pulled down.

#### **Programmable Oscillator**

The TD1457C oscillating frequency is set by an external resistor, RFREQ from the FREQ pin to ground. The value of RFREQ can be calculated from:

$$R_{FREQ}(k\Omega) = \frac{100000}{f_s(kHz)} - 5$$

To get fsw=500kHz, R<sub>FREQ</sub>=195kΩ.

TD1457C

### **Application information**

#### **Setting the Output Voltage**

The output voltage is set using a resistive voltage divider from the output voltage to FB pin. The voltage divider divides the output voltage down to the feedback voltage by the ratio:

$$V_{FB} = V_{OUT} \times \frac{R2}{R1 + R2}$$

Thus the output voltage is:

$$V_{OUT} = V_{FB} \times \frac{R1 + R2}{R2}$$

For example, the value for R2 can be  $10k\Omega$ . With this value, R1 can be determined by:

R1=12.5 ×

$$(V_{OUT}$$

-0.8) $(K\Omega)$

For example, for a 3.3V output voltage, R2 is  $10k\Omega$ , and R1 is  $31.6k\Omega$ .

#### Inductor

The inductor is required to supply constant current to the output load while being driven by the switched input voltage. A larger value inductor will result in less ripple current that will result in lower output ripple voltage. However, the larger value inductor will have a larger physical size, higher series resistance, and/or lower saturation current.

A good rule for determining the inductance to use is to allow the peak-to-peak ripple current in the inductor to be approximately 30% of the maximum switch current limit. Also, make sure that the peak inductor current is below the maximum switch current limit. The inductance value can be calculated by:

$$L1 = \frac{V_{OUT}}{f_s \times \Delta I_L} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

Where VOUT is the output voltage, VIN is the input voltage, fS is the switching frequency, and  $\Delta IL$  is the peak-to-peak inductor ripple current.

Choose an inductor that will not saturate under the maximum inductor peak current. The peak inductor current can be calculated by:

$$I_{LP} = I_{LOAD} + \frac{V_{OUT}}{2 \times f_8 \times L1} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Where  $I_{LOAD}$  is the load current.

Table 1 lists a number of suitable inductors from various manufacturers. The choice of which style inductor to use mainly depends on the price vs. size requirements and any EMI requirement.

### **Output Rectifier Diode**

The output rectifier diode supplies the current to the inductor when the high-side switch is off. To reduce losses due to the diode forward voltage and recovery times, use a Schottky diode.

Choose a diode whose maximum reverse voltage rating is greater than the maximum input voltage, and whose current rating is greater than the maximum load current. Table 2 lists example Schottky diodes and manufacturers.

Table 2—Diode Selection Guide

| Diodes      | Voltage/<br>Current<br>Rating | Manufacturer |  |

|-------------|-------------------------------|--------------|--|

| B290-13-F   | 90V, 2A                       | Diodes Inc.  |  |

| B380-13-F   | 80V, 3A                       | Diodes Inc.  |  |

| CMSH2-100M  | 100V, 2A                      | Central Semi |  |

| CMSH3-100MA | 100V, 3A                      | Central Semi |  |

#### **Input Capacitor**

The input current to the step-down converter is discontinuous, therefore a capacitor is required to supply the AC current to the step-down converter while maintaining the DC input voltage. Use low ESR capacitors for the best performance. Ceramic capacitors are preferred, but tantalum or low-ESR electrolytic capacitors may also suffice. For simplification, choose the input capacitor with RMS current rating greater than half of the maximum load current. The input capacitor (C1) can be electrolytic, tantalum or ceramic.

When using electrolytic or tantalum capacitors, a small, high quality ceramic capacitor, i.e.  $0.1\mu F$ , should be placed as close to the IC as possible. When using ceramic capacitors, make sure that they have enough capacitance to provide sufficient charge to prevent excessive voltage ripple at input. The input voltage ripple caused by capacitance can be estimated by:

TD1457C

$$\Delta V_{IN} = \frac{I_{LOAD}}{f_8 \times C1} \times \frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

#### **Output Capacitor**

The output capacitor (C2) is required to maintain the DC output voltage. Ceramic, tantalum, or low ESR electrolytic capacitors are recommended. Low ESR capacitors are preferred to keep the output voltage ripple low. The output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_S \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times \left(R_{ESR} + \frac{1}{8 \times f_S \times C2}\right)$$

Where L is the inductor value and RESR is the equivalent series resistance (ESR) value of the output capacitor.

In the case of ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance. The output voltage ripple is mainly caused by the capacitance. For simplification, the output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{8 \times f_{S}^{2} \times L \times C2} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

In the case of tantalum or electrolytic capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated to:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_{S} \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times R_{ESR}$$

The characteristics of the output capacitor also affect the stability of the regulation system. The TD1457C can be optimized for a wide range of capacitance and ESR values.

#### **Compensation Components**

TD1457C employs current mode control for easy compensation and fast transient response. The system stability and transient response are controlled through the COMP pin. COMP pin is the output of the internal error amplifier. A series capacitor-resistor combination sets a pole-zero combination to control the characteristics of the control system. The DC gain of the voltage feedback loop is given by:

$$A_{VDC} = R_{LOAD} \times G_{CS} \times A_{VEA} \times \frac{V_{FB}}{V_{OUT}}$$

Where AVEA is the error amplifier voltage gain, 400V/V; GCS is the current sense transconductance, 5.6A/V; RLOAD is the

load resistor value.

The system has two poles of importance. One is due to the compensation capacitor (C3), the output resistor of error amplifier. The other is due to the output capacitor and the load resistor. These poles are located at:

$$f_{pl} = \frac{G_{EA}}{2\pi \times C3 \times A_{VEA}}$$

$$f_{p_2} = \frac{1}{2\pi \times C2 \times R_{LOAD}}$$

Where, GEA is the error amplifier transconductance,  $120\mu A/V$ .

The system has one zero of importance, due to the compensation capacitor (C3) and the compensation resistor (R3). This zero is located at:

$$f_{z1} = \frac{1}{2\pi \times C3 \times R3}$$

The system may have another zero of importance, if the output capacitor has a large capacitance and/or a high ESR value. The zero, due to the ESR and capacitance of the output capacitor, is located at:

$$f_{\text{ESR}} = \frac{1}{2\pi \times C2 \times R_{\text{ESR}}}$$

In this case, a third pole set by the compensation capacitor (C5) and the compensation resistor (R3) is used to compensate the effect of the ESR zero on the loop gain. This pole is located at:

$$f_{p3} = \frac{1}{2 \pi \times C \times R 3}$$

The goal of compensation design is to shape the converter transfer function to get a desired loop gain. The system crossover frequency where the feedback loop has the unity gain is important. Lower crossover frequencies result in slower line and load transient responses, while higher crossover frequencies could cause system unstable. A good rule of thumb is to set the crossover frequency to approximately one-tenth of the switching frequency.

To optimize the compensation components for conditions not listed in Table 3, the following procedure can be used.

1. Choose the compensation resistor (R3) to set the desired crossover frequency. Determine the R3 value by the following equation:

### TD1457C

$$R.3 = \frac{2\pi \times C.2 \times f_{C}}{G_{EA} \times G_{CS}} \times \frac{V_{OUT}}{V_{FB}}$$

Where  $f_C$  is the desired crossover frequency.

2. Choose the compensation capacitor (C3) to achieve the desired phase margin. For applications with typical inductor values, setting the compensation zero, fZ1, below one forth of the crossover frequency provides sufficient phase margin. Determine the C3 value by the following equation:

$$C3 > \frac{4}{2\pi \times R3 \times f_C}$$

3. Determine if the second compensation capacitor (C5) is required. It is required if the ESR zero of the output capacitor is located at less than half of the switching frequency, or the following relationship is valid:

$$\frac{1}{2\pi \times C2 \times R_{\text{ESR}}} < \frac{f_{\text{S}}}{2}$$

If this is the case, then add the second compensation capacitor (C5) to set the pole fP3 at the location of the ESR zero. Determine the C5 value by the equation:

$$C5 = \frac{C2 \times R_{ESR}}{R3}$$

#### **High Frequency Operation**

The switching frequency of TD1457C can be programmed up to 1MHz by an external resistor.

The minimum on time of TD1457C is about 100ns(typ). Pulse skipping operation can be seen more easily at higher switching frequency due to the minimum on time.

Since the internal bootstrap circuitry has higher impedance, which may not be adequate to charge the bootstrap capacitor during each (1-D)×Ts charging period, an external bootstrap charging diode is strongly recommended if the switching frequency is about 1MHz (see External Bootstrap Diode section for detailed implementation information). With higher switching frequencies, the inductive reactance (XL) of capacitor comes to dominate, so that the ESL of input/output capacitor determines the input/output ripple

input/output capacitor determines the input/output ripple voltage at higher switching frequency. As a result of that, high frequency ceramic capacitor is strongly recommended as input decoupling capacitor and output filtering capacitor for such high frequency operation.

Layout becomes more important when the device switches at higher frequency. It is essential to place the input decoupling capacitor, catch diode and the TD1457C (VIN pin, SW pin and PGND) as close as possible, with traces that are very short and fairly wide. This can help to greatly reduce the voltage spike on SW node, and lower the EMI noise level as well.

Try to run the feedback trace as far from the inductor and noisy power traces as possible. It is often a good idea to run the feedback trace on the side of the PCB opposite of the inductor with a ground plane separating the two. The compensation components should be placed closed to the TD1457C. Do not place the compensation components close to or under high dv/dt SW node, or inside the high di/dt power loop. If you have to do so, the proper ground plane must be in place to isolate those. Switching loss is expected to be increased at high switching frequency. To help to improve the thermal conduction, a grid of thermal vias can be created right under the exposed pad. It is recommended that they be small (15mil barrel diameter) so that the hole is essentially filled up during the plating process, thus aiding conduction to the other side. Too large a hole can cause 'solder wicking' problems during the reflow soldering process. The pitch (distance between the centers) of several such thermal vias in an area is typically 40mil.

#### **External Bootstrap Diode**

An external bootstrap diode may enhance the efficiency of the regulator. In below cases, an external BST diode is recommended from the 5V to BST pin:

- There is a 5V rail available in the system;

- VIN is no greater than 5V;

- VOUT is between 3.3V and 5V;

This diode is also recommended for high duty cycle operation (when VOUT/VIN > 65%) applications.

The bootstrap diode can be a low cost one such as IN4148 or BAT54.

TD1457C

At no load or light load, the converter may operate in pulse skipping mode in order to maintain the output voltage in regulation. Thus there is less time to refresh the BS voltage. In order to have enough gate voltage under such operating conditions, the difference of VIN –VOUT should be greater than 3V. For example, if the VOUT is set to 3.3V, the VIN needs to be higher than 3.3V+3V=6.3V to maintain enough BST voltage at no load or light load. To meet this requirement, EN pin can be used to program the input UVLO voltage to VOUT+3V.

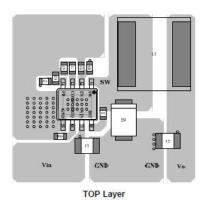

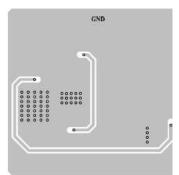

### **PCB Layout Note**

PCB layout is very important to achieve stable operation. It is highly recommended to duplicate EVB layout for optimum performance.

If change is necessary, please follow these guidelines and take Figure 5 for reference.

- 1) Keep the path of switching current short and minimize the loop area formed by Input cap, high-side MOSFET and external switching diode..

- 2) Bypass ceramic capacitors are suggested to be put close to the VIN Pin.

- 3) Ensure all feedback connections are short and direct. Place the feedback resistors and compensation components as close to the chip as possible.

- 4) Route SW away from sensitive analog areas such as FB.

- 5) Connect IN, SW, and especially GND respectively to a large copper area to cool the chip to improve thermal performance and long-term reliability.

Bottom Layer

## TD1457C

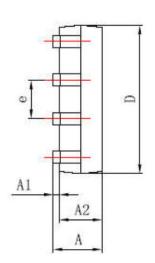

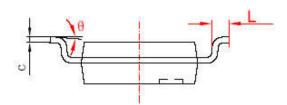

## **Package Information**

**ESOP-8** Package Outline Dimensions

|    | Dimensions I | Dimensions In Millimeters |        | s In Inches |

|----|--------------|---------------------------|--------|-------------|

|    | Min          | Max                       | Min    | Max         |

| Α  | 1. 350       | 1.750                     | 0.053  | 0.069       |

| A1 | 0.050        | 0. 150                    | 0.004  | 0.010       |

| A2 | 1. 350       | 1.550                     | 0.053  | 0.061       |

| b  | 0. 330       | 0.510                     | 0.013  | 0.020       |

| С  | 0.170        | 0. 250                    | 0.006  | 0.010       |

| D  | 4. 700       | 5. 100                    | 0. 185 | 0. 200      |

| D1 | 3. 202       | 3. 402                    | 0. 126 | 0. 134      |

| E  | 3. 800       | 4. 000                    | 0. 150 | 0. 157      |

| E1 | 5. 800       | 6. 200                    | 0. 228 | 0. 244      |

| E2 | 2. 313       | 2. 513                    | 0. 091 | 0.099       |

| е  | 1. 270 (BSC) |                           | 0.050  | O (BSC)     |

| Ĺ  | 0.400        | 1. 270                    | 0.016  | 0.050       |

| θ  | 0°           | 8°                        | 0°     | 8°          |

TD1457C

**Design Notes**